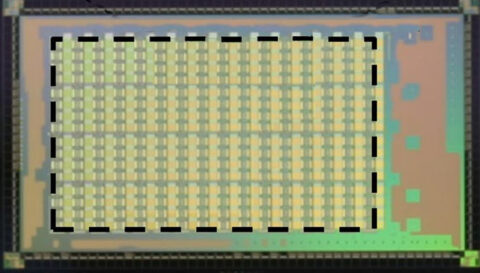

During the last reporting period, the main focus was on transferring the metal-ferroelectric-metal capacitor stack from the lab, having a diameter of about 100 μm, to memory arrays with 100-1000 times smaller feature sizes. Concurrently, optimizing the film and film stack properties to improve the reliability of the ferroelectric capacitor according to industry specifications was addressed. The goal is to develop back-end-of-line compatible capacitors with a maximum thermal budget of 500°C or below. The ferroelectric material of choice is an atomic layer deposited Hf0.5Zr0.5O2. The activity was conducted with industrial partners, including LETI and ST, Sony, and Intel. 16, 64, and 1000 kbit-sized memory arrays with Hf0.5Zr0.5O2-based capacitors were realized with a high yield on 200 mm hardware.

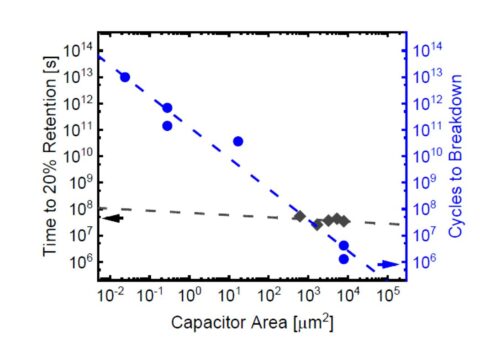

The polarization hysteresis of Hf0.5Zr0.5O2 -based capacitors showed a maximum remanent polarization of about 25 μC/cm². In addition, the influence of interface layers with Hf0.5Zr0.5O2 on the field cycling behavior was examined, and stable cycling behavior of up to 1010 cycles was achieved. Scaling of the devices below 1 μm² improved cycling endurance. Values can be extrapolated beyond 1012 cycles for 2.5 MV/cm² target field conditions. (Figure 1) Wake-up, internal bias fields, fatigue, imprint, and retention effects in Hf0.5Zr0.5O2 are generally dominated by charge trapping effects at defects mainly located at the Hf0.5Zr0.5O2/electrode interface. Furthermore, depolarization effects can be caused by nonpolar phases. The duration of the ALD oxidant pulse strongly impacted the ferroelectric properties and device reliability, which was then used to optimize ALD processing. Due to the resulting voltage-time trade-off to achieve > 90% domain switching after 20 ns, a 2.5 MV/cm² field must be applied to layers with below 10 nm thick films.

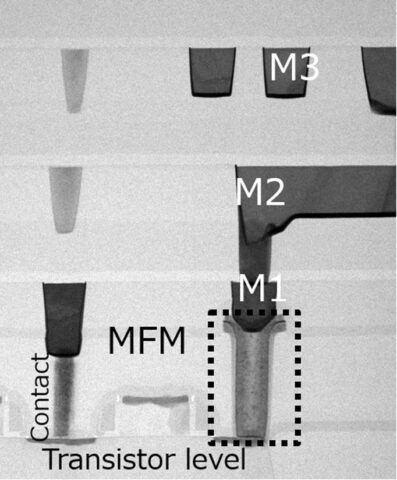

Development partners introduced the Hf0.5Zr0.5O2 ferroelectric material into their memory arrays and reached a field cycling endurance > 1011 for sub-1 μm 3D capacitor structures (Figure 2). Sense amplifiers read out stored polarization states and have a good read voltage margin with a 2.5 V operation voltage. They confirmed an operating speed of about 20 ns for 16 to 1000 kbit memory arrays (Figure 3).

Future studies will focus on further understanding the structural basis of the ferroelectric properties and their impact on the ferroelectric switching behavior to improve cycling performance for introduction into larger memory arrays.

Cooperation:

CEA Saclay / CEA-LETI (France), ST Microelectronics (France), National Institute of Materials Physics (Romania), EPFL (Switzerland), Ecole Centrale De Lyon (France), NCSR „DEMOKRITOS“ (Greece), Forschungszentrum Jülich (Germany), Sony (Japan)